#### We will consider a number of issues related to bus architectures in digital systems. **Topic 10** Useful references: "Bus Architecture of a System on a Chip with User-Configurable System **Bus Architecture &** Logic", Steven Winegarden, IEEE JOURNAL OF SOLID-STATE CIRCUITS, Interconnects VOL. 35, NO. 3, MARCH 2000, p425-433. "AMBA: ENABLING REUSABLE ON-CHIP DESIGNS". David Flvnn, IEEE Micro, July/August 1997. AMBA<sup>™</sup> Specification (Rev 2.0), ARM Ltd., 1999 Peter Cheung The CoreConnect Bus Architecture. IBM. Department of Electrical & Electronic Engineering Imperial College London • VSI Alliance Architecture Document, version 1.0, 1997. • Draft Chapter, "System-on-Chip", Flynn & Luk URL: www.ee.imperial.ac.uk/pcheung/ E-mail: p.cheung@imperial.ac.uk PYKC 6-Mar-08 Topic 10 Slide 1 PYKC 6-Mar-08 Topic 10 Slide 2 E3.05 Digital System Design E3.05 Digital System Design

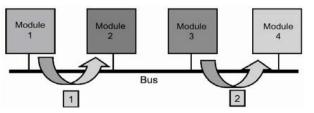

#### Basic concepts: Bus basics: order and broadcast properties

• Communications on buses must be in strict order: serial nature of bus

• It can broadcast a transaction - sending to multiple components simultaneously

### Basic concepts: Cycles, messages and transactions

Introductions & Sources

- Buses operate in units of cycles, Messages and transactions.

- *Cycles*: A message requires a number of clock cycles to be sent from sender to receiver over the bus.

- *Messag*e: These are logical unit of information. For example, a write message contains an address, control signals and the write data.

- *Transactio*n: A transaction consists of a sequence of messages which together form a transaction. For example, a memory read requires a memory read message and a reply with the requested data.

Topic 10 Slide 3

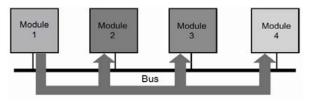

## Synchronous vs Asynchronous

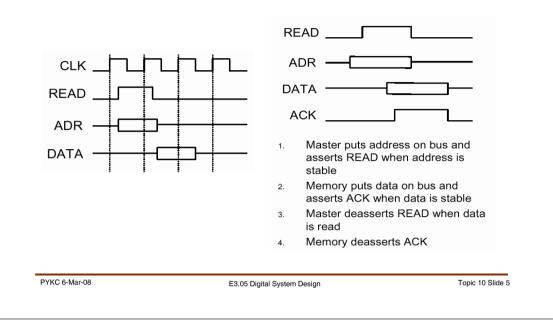

#### Basic concepts: Bus arbitration

- Only one bus master can control the us.

- Need some way of deciding who is master may use a bus arbiter:

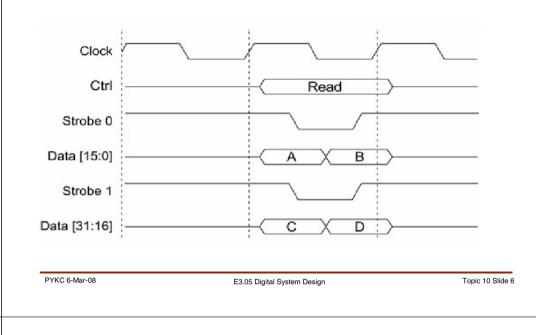

### Basic concepts: Typical Source Synchronous Data Transfer

#### Basic concepts: Bus pipelining

- A transaction may take multiple cycles

- Overlap multiple transaction through pipelining:

|           | 1  | 2   | 3   | 4   | 5     | 6     | 7   | 8     | 9   | 10    | 11  | 12 | 13    | 14    | 15 |

|-----------|----|-----|-----|-----|-------|-------|-----|-------|-----|-------|-----|----|-------|-------|----|

| 1. Read   | AR | ARB | AG  | RQ  | Р     | RPLY  |     |       |     |       |     |    |       |       |    |

| 2. Write  |    | AR  | ARB | AG  | Stall | Stall | RQ  | ACK   |     |       |     |    |       |       |    |

| 3. Write  |    |     | AR  | ARB | Stall | Stall | AG  | Stall | RQ  | ACK   |     |    |       |       |    |

| 4. Read   |    |     |     | AR  | Stall | Stall | ARB | Stall | AG  | Stall | RQ  | Ρ  | RPLY  | RQ    |    |

| 5. Read   |    |     |     |     |       |       | AR  | Stall | ARB | Stall | AG  | RQ | Р     | RPLY  |    |

| 6. Read   |    |     |     |     |       |       |     |       | AR  | Stall | ARB | AG | Stall | Stall | RQ |

| Due hurre |    |     |     |     |       |       |     |       |     |       |     |    |       |       |    |

| Bus busy  |    |     |     |     |       |       |     |       |     |       |     |    |       |       |    |

Topic 10 Slide 7

PYKC 6-Mar-08

#### **Basic concepts: Split-transaction bus**

- A bus transaction can be divided into two or more phases, e.g.

- "Request" phase

#### 1. Read • "Reply" phase AR ARB AG RQ 2. Write AR ARB AG RQ • These can be split into two separate sub-transactions, which may or may 3. Write not happen consecutively. If split, these must compete for the bus by AR ARB AG RQ 4. Read arbitration. AR ARB AG RPLY 1. Reply 5. Read AR ARB Stall Stall Stall Stall AG RQ ARB AG RPL AR 2. Reply 6. Read AR ARB Stall Stall Stall Stall AG RQ ARB AG RPLY AR 3. Reply ARB 4. Reply AR AG RPLY AR 5. Reply ARB AG AR 6. Reply ARB Bus busy PYKC 6-Mar-08 Topic 10 Slide 9 PYKC 6-Mar-08 Topic 10 Slide 10 E3.05 Digital System Design E3.05 Digital System Design **Basic concepts: Basic concepts:** Pipelined only bus vs split-transaction bus **Burst transfer mode Pipelined Bus** ARB ARB ARB ARB Adr Data Adr Data Adr Data Cmd Adr Data Cmd Cmd Cmd 2 3 12 13 5 10 11 14 Δ 9 Request RQ A RP A 1. Trans ARB RP B 2. Trans RQ B Cmd Adr Data Data Data Data RP C RQ C 3. Trans Burst Request Split-Transaction Bus 1. Trans RQ A RP A Gnt A Gnt B Res A Arbitration RQ B RP B 2. Trans Adr Data Data Data Data Data Data Data Cmd Adr Data Message A Cmd Adr Data Message B RQ C RP C 3. Trans PYKC 6-Mar-08 PYKC 6-Mar-08 Topic 10 Slide 11 E3.05 Digital System Design

**Basic concepts:**

**Split-transaction bus**

8

9

10 11 12

13

14

15

6

2

ARB

3

AG

4

RQ

5

1

AR

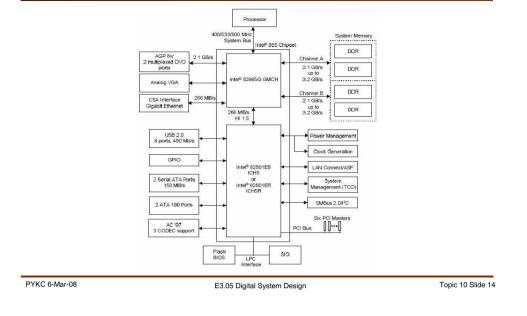

## **Bus hierarchy**

## **Bus bandwidth**

| Bus            | Width<br>(bits) | Bus Speed (MHz) | Bus Bandwidth<br>(MBytes/sec) |  |  |

|----------------|-----------------|-----------------|-------------------------------|--|--|

| 8-bit ISA      | 8               | 8.3             | 7.9                           |  |  |

| 16-bit ISA     | 16              | 8.3             | 15.9                          |  |  |

| EISA           | 32              | 8.3             | 31.8                          |  |  |

| VLB            | 32              | 33              | 127.2                         |  |  |

| PCI            | 32              | 33              | 127.2                         |  |  |

| 64-bit PCI 2.1 | 64              | 66              | 508.6                         |  |  |

| AGP            | 32              | 66              | 254.3                         |  |  |

| AGP (x2 mode)  | 32              | 66x2            | 508.6                         |  |  |

| AGP (x4 mode)  | 32              | 66x4            | 1,017.3                       |  |  |

PYKC 6-Mar-08

E3.05 Digital System Design

Topic 10 Slide 13

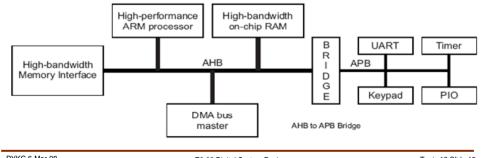

## **AMBA** bus

- Based around ARM processor

- AHB Advanced High-Performance Bus

- > Pipelining of Address / Data

- > Split Transactions

- ► Multiple Masters

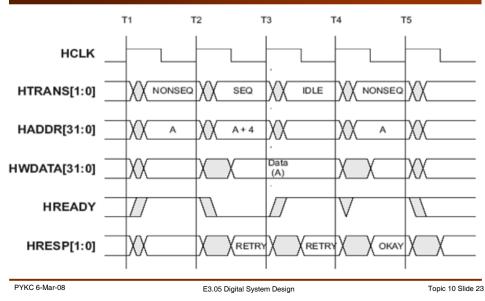

- APB Advanced Peripheral Bus

- ► Low Power / Bandwidth Peripheral Bus

# **AMBA Bus Design Goals**

- Encourages modular design and design reuse

- Well defined interface protocol, clocking and reset

- Low-power support (helped by two-level partitioning)

- On-chip test access built-in structure for testing modules connected on the bus

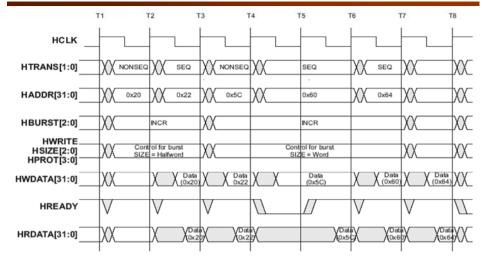

- Transactions on AHB

- Bus master obtain access to the bus

- Bus master initiates transfer

- Bus slave provides response

# **AMBA** bus arbitration

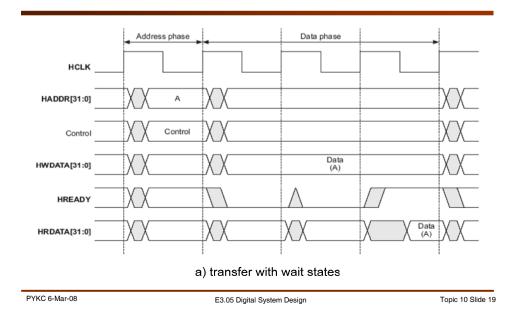

# **AHB Transfer with wait states**

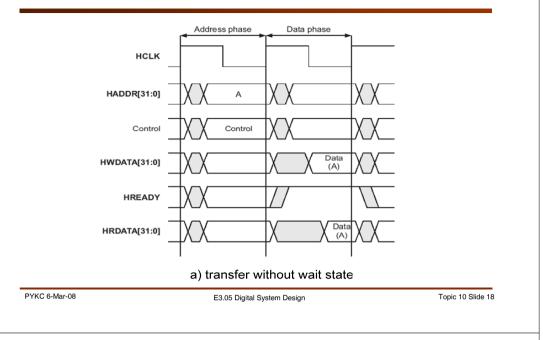

# Simple AHB Transfer

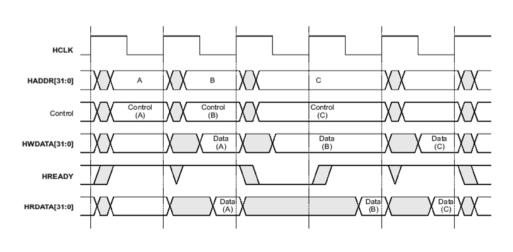

# **Multiple transfers with Pipelining**

PYKC 6-Mar-08

## Burst mode transfer (undefined length)

E3.05 Digital System Design

## **Slave Transfer Responses**

Complete transfer immediately (single cycle transfer)

Insert one or more wait states to allow completion

♦ 1.

2.

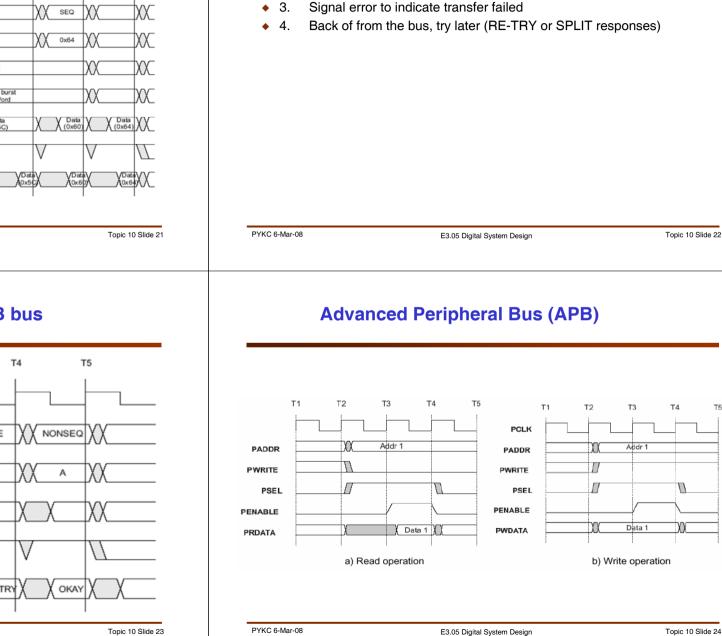

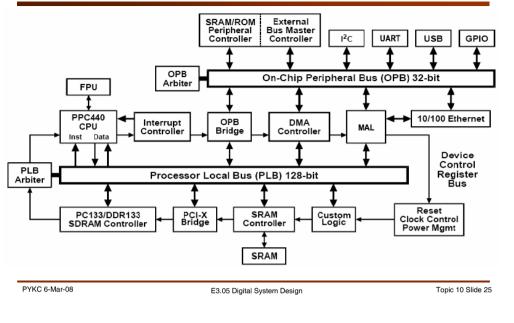

# **Retry Responses on the AHB bus**

PYKC 6-Mar-08

$\Box$

T5

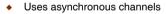

# **IBM CoreConnect Bus**

# **CoreConnect vs AMBA**

|                      | IBM CoreConnect<br>Processor Local Bus                                                                                               | ARM AMBA 2.0<br>AMBA High-performance Bus                                                     |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| Bus Architecture     | 32-, 64-, and 128-bits<br>Extendable to 256-bits                                                                                     | 32-, 64-, and 128-bits                                                                        |  |  |

| Data Buses           | Separate Read and Write                                                                                                              | Separate Read and Write                                                                       |  |  |

| Key Capabilities     | Multiple Bus Masters<br>4 Deep Read Pipelining<br>2 Deep Write Pipelining<br>Split Transactions<br>Burst Transfers<br>Line Transfers | Multiple Bus Masters<br>Pipelining<br>Split Transactions<br>Burst Transfers<br>Line Transfers |  |  |

|                      | On-Chip Peripheral Bus                                                                                                               | AMBA Advanced Peripheral Bus                                                                  |  |  |

| Masters<br>Supported | Supports Multiple Masters                                                                                                            | Single Master: The APB Bridge                                                                 |  |  |

| Bridge Function      | Master on PLB or OPB                                                                                                                 | APB Master Only                                                                               |  |  |

| Data Buses           | Separate Read and Write                                                                                                              | Separate or 3-state                                                                           |  |  |

| E3.05 Digital System Design | Topic 10 Slide 25 | PYKC 6-Mar-08 | E3.05 Digital System Design | Topic 10 Slide 26 |

|-----------------------------|-------------------|---------------|-----------------------------|-------------------|

|                             |                   |               |                             |                   |

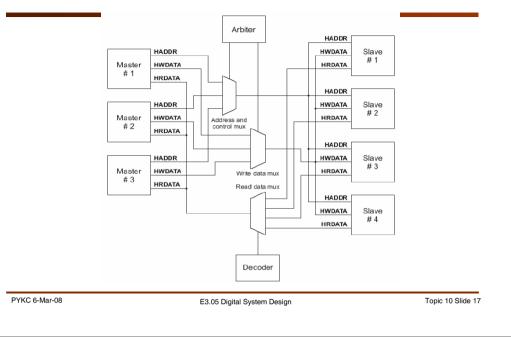

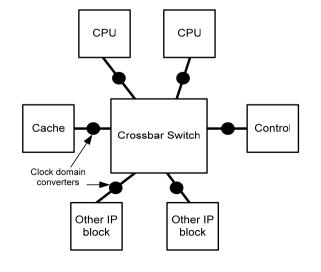

## **Crossbar Switch Approach**

- Different modules can run at different clock frequency

- Globally Asychronous, Locally Synchronous (GALS) system

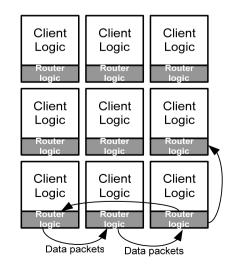

# Network-on-chip approach

- Array of tiles

- Each tile contains client logic and router logic

- 2-D mesh topology

- Uses data packets, not wires, for communication

- Predictable delay, and noise

PYKC 6-Mar-08

Topic 10 Slide 27

PYKC 6-Mar-08